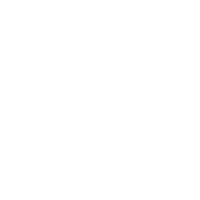

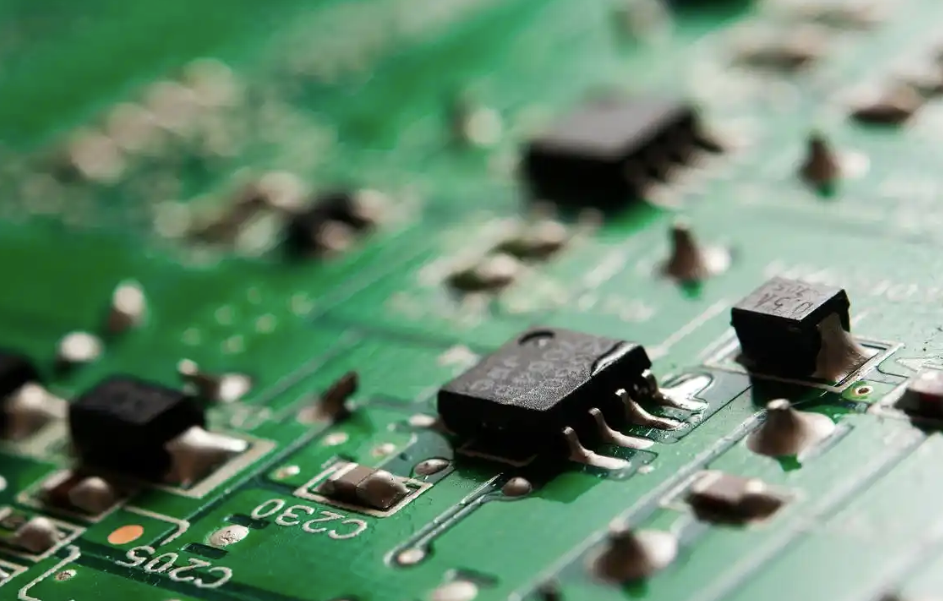

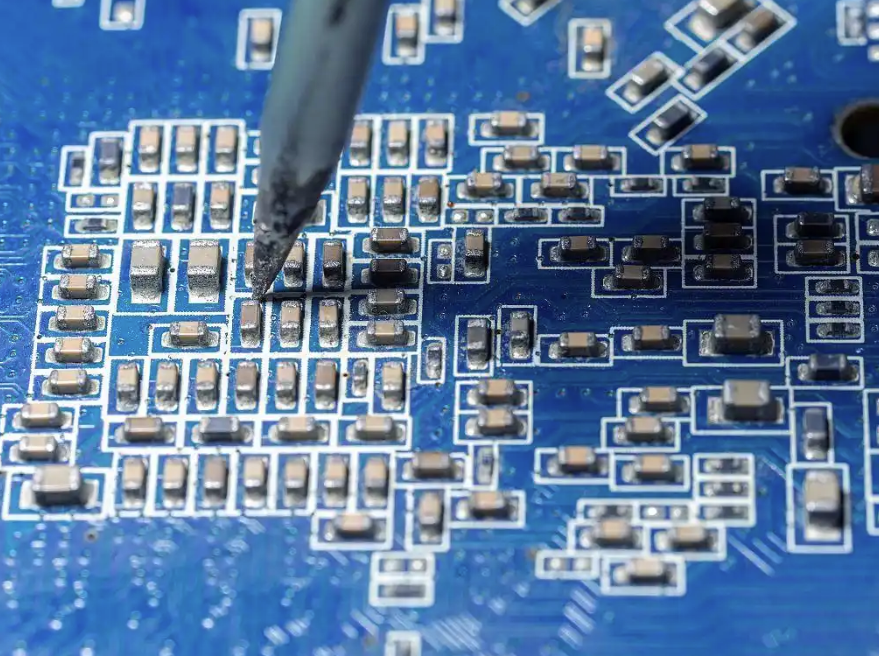

In dem explosiven Wachstum der tragbaren elektronischen Geräte, das Internet der Dinge Terminal Form weiter zu entwickeln, Halbleiter-Entwicklung Bord als Kern Träger des elektronischen Systems ist mit der dreifachen Herausforderung der "kleineren Größe, höhere Integration, stärkere Leistung". Als Kernprozess der PCBA-Verarbeitung, SMT-Bestückungstechnologie durch die Komponente Miniaturisierung Anpassung, High-Density-Montage-Prozess-Innovation und dreidimensionale Integration Fähigkeit Durchbrüche, um den wichtigsten Motor für die Entwicklung Board Miniaturisierung Probleme zu knacken, um seine Unterhaltungselektronik, Automobilelektronik, Luft-und Raumfahrt und anderen Bereichen zu fördern, um die Form der Revolution zu erreichen. Zunächst möchten wir über die physikalischen Grundlagen der Miniaturisierung von elektrischen Bauteilen sprechen. Der Hauptvorteil der SMT-Bestückungstechnologie besteht darin, dass sie die Größenbeschränkungen der traditionellen Durchgangslochbestückung durchbricht und einen zuverlässigen physikalischen Träger für elektronische Ultra-Miniaturbauteile bietet. Moderne Bestückungsautomaten können Chipkomponenten der Größe 0201 (0,6mm x 0,3mm) oder sogar 01005 (0,4mm x 0,2mm) mit einer Bestückungsgenauigkeit von ±50μm präzise platzieren, um die Ausrichtungsanforderungen von QFP-Gehäusen mit 0,3mm Pinabstand zu erfüllen. Dank der Nectec-Bestückungsautomaten der Serie NT-P5 ist eine flexible Verarbeitung von Chip-Bauteilen der Größe 0201 mit Hilfe der modularen Design-Support-Transformationstechnologie möglich. Diese Fähigkeit ermöglicht es Halbleiter-Entwicklungsplatinen, die Dichte des Komponenten-Layouts um das 5-10-fache zu erhöhen: In Smartphone-Basisband-Entwicklungsplatinen können durch die Kombination von MLCC-Kondensatoren der Größe 0402 und LGA-Chips im 0,5 mm-Pitch-Gehäuse auf einem Quadratzentimeter mehr als 50 aktive und 200 passive Komponenten integriert werden, was einer mehr als 3-fachen Integrationsdichte im Vergleich zum traditionellen Bestückungsprozess entspricht.

Im nächsten Thema werden wir uns mit der praktischen Anwendung dieser neuen SMT-Technologie befassen. Dabei möchten wir uns auf drei Bereiche konzentrieren: Unterhaltungselektronik, Automobilelektronik und Luft- und Raumfahrtindustrie. Zunächst zum Thema Unterhaltungselektronik. Bei der Entwicklungsplatine für Smartwatches werden mit dem SMT-Verfahren die 0,4 mm Dicke der flexiblen Leiterplatte und die 0,4 mm Höhe der ultradünnen Komponenten realisiert, wie z. B. mit unserer NT-L12-Bestückungsmaschine von Nectec, mit der Technologie der gekrümmten Oberflächenmontage (Montagewinkelabweichung <1°), so dass die gesamte Platine mit einem Radius von <5 mm gebogen werden kann, was perfekt an das Design von runden Uhrengehäusen angepasst ist. Durch die Kontrolle der Bauteilhöhe (das höchste Bauteil ≤ 1,2 mm) wird die Gesamtdicke der Entwicklungsplatine auf weniger als 2,5 mm komprimiert, wodurch 30% Platz für die Batterie und die Sensoren frei werden. Für Automobilelektronik, Automotive ADAS Entwicklungsboard mit Blick auf hohe Temperatur (-40 ℃ ~ +125 ℃), Vibration (50g Beschleunigung) der rauen Umgebung, SMT-Technologie durch Miniaturisierung zu einem kompakten Layout zu erreichen: die Verwendung von 0.5mmpitch BGA-Paket-Chip, mit dem Boden der Füllung Prozess (Füllgeschwindigkeit 50mm / s), in der 100mm × 100mm Substrat-Integration von 6 AI-Chip mit 20 Sensor-Schnittstelle, ist das Volumen von 60% im Vergleich mit der traditionellen Lösung reduziert, und zur gleichen Zeit, die Wärmeableitung Effizienz wird durch die Optimierung der Komponente Abstand (≥0,5mm) verbessert.

Für die Luft-und Raumfahrtindustrie, Satelliten-Nutzlast Entwicklung Bretter sind empfindlich auf das Gewicht (Kosten pro Gramm>$1000), SMT-Technologie durch leichtes Material Anpassung an einen Durchbruch zu erreichen: die Verwendung von Aluminium-basierte PCB (Dichte 2,7g/cm³) anstelle der traditionellen FR-4 Substrat, mit 0,1mm Dicke der ultra-dünnen Chip (Gewicht <0.1g) Montage, so dass das Gewicht der Flächeneinheit, um das Gewicht von 40% zu reduzieren. Durch den Algorithmus zur Optimierung des Komponentenlayouts (genetischer Algorithmus) werden 10 Schichten von Schaltkreisverbindungen auf einem 200mm×150mm großen Substrat realisiert, was im Vergleich zum manuellen Layout 20% Platz spart.