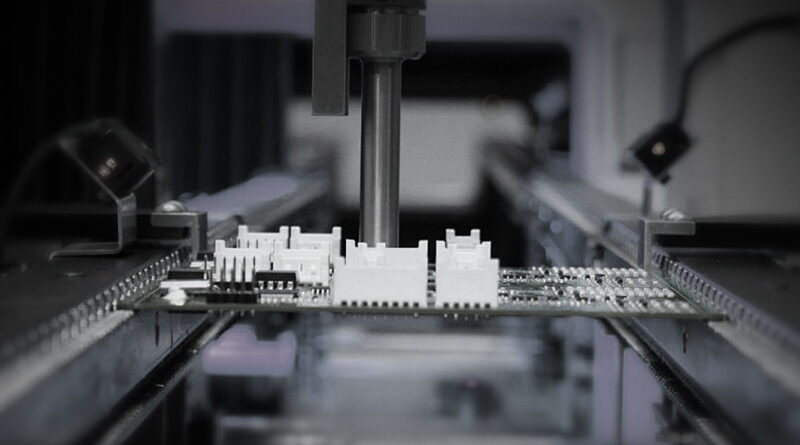

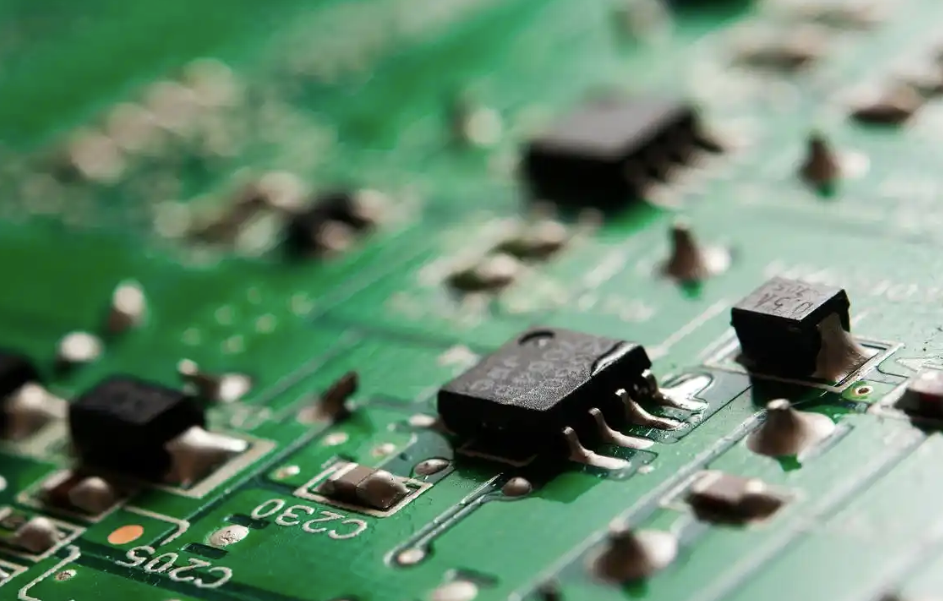

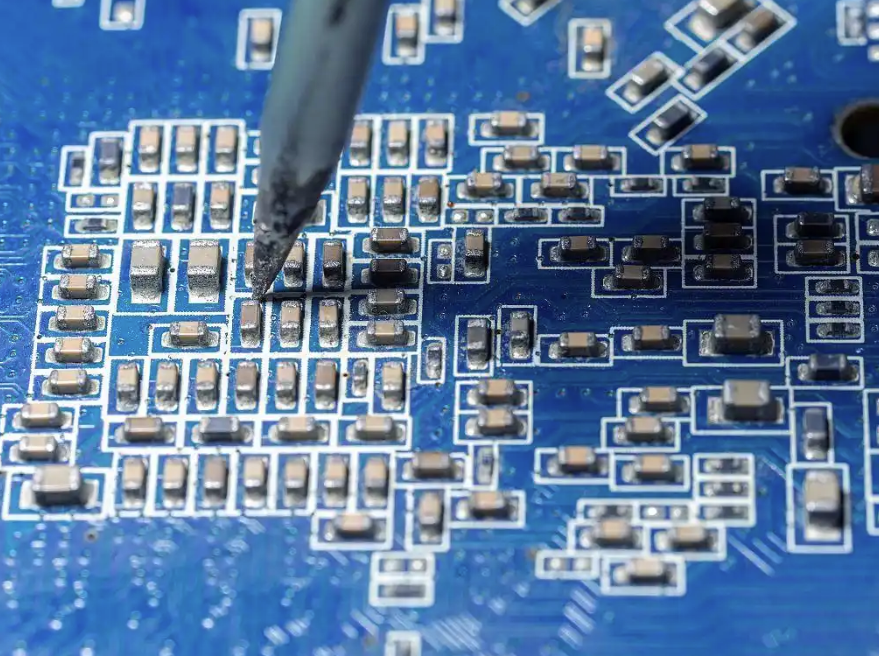

În creșterea explozivă a dispozitivelor electronice portabile, forma terminalului Internet of Things continuă să evolueze, placa de dezvoltare a semiconductorilor ca suport de bază al sistemului electronic se confruntă cu tripla provocare a "dimensiunii mai mici, integrării mai mari, performanței mai puternice". Ca proces de bază al procesării PCBA, tehnologia de plasare SMT prin adaptarea miniaturizării componentelor, inovarea procesului de montare de înaltă densitate și progresele capacității de integrare tridimensională, pentru a deveni motorul cheie pentru a rezolva problemele de miniaturizare a plăcii de dezvoltare, pentru a promova electronicele sale de consum, electronicele auto, aerospațiale și alte domenii pentru a obține forma revoluției. În primul rând, am dori să discutăm despre fizica din spatele bazei miniaturizării componentelor electrice. Avantajul principal al tehnologiei de plasare SMT este că aceasta depășește limitele de dimensiune ale inserției tradiționale prin găuri și oferă un suport fizic fiabil pentru componentele electronice ultra-miniaturizate. Mașinile moderne de plasare pot plasa cu acuratețe componente de cip de dimensiunea 0201 (0,6 mm x 0,3 mm) sau chiar 01005 (0,4 mm x 0,2 mm), cu o precizie de plasare de ±50μm, pentru a îndeplini cerințele de aliniere ale pachetelor QFP cu pas de 0,3 mm. Datorită mașinii de preluare și plasare Nectec din seria NT-P5, aceasta este capabilă să realizeze procesarea flexibilă a componentelor cipurilor de dimensiunea 0201 utilizând tehnologia de transformare a suportului de proiectare modulară. Această capacitate permite plăcilor de dezvoltare a semiconductorilor să crească densitatea de dispunere a componentelor de 5-10 ori: în plăcile de dezvoltare a benzii de bază pentru smartphone-uri, prin combinarea condensatoarelor MLCC de dimensiune 0402 și a cipurilor ambalate LGA cu pas de 0,5 mm, unitatea de centimetru pătrat poate fi integrată cu peste 50 de componente active și 200 de componente pasive, ceea ce reprezintă o densitate de integrare de peste 3 ori mai mare comparativ cu procesul tradițional de inserție.

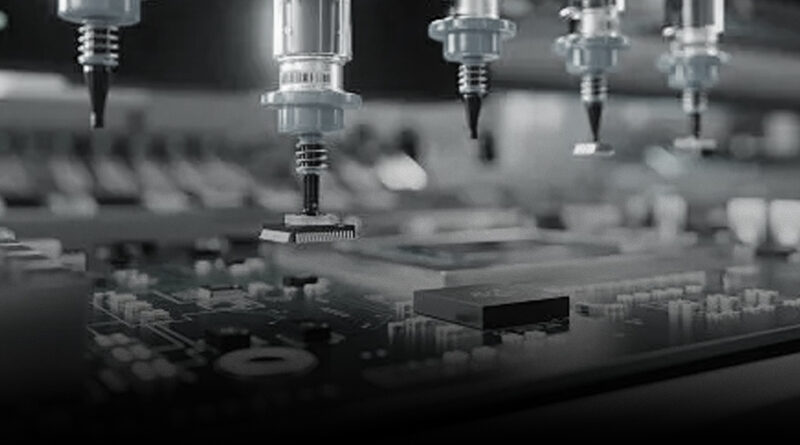

În subiectul următor, vom discuta despre aplicarea în viața reală a acestui progres al tehnologiei SMT. Există trei domenii asupra cărora am dori să ne concentrăm: electronica de consum, electronica auto și industria aerospațială. Mai întâi să discutăm despre electronica de consum. În placa de dezvoltare a ceasului inteligent, procesul SMT realizează grosimea de 0,4 mm a PCB-ului flexibil și înălțimea de 0,4 mm a componentelor ultra-subțiri, cum ar fi mașina noastră Nectec NT-L12 pick and place, cu tehnologia de montare pe suprafață curbată (abaterea unghiului de montare <1°), astfel încât întreaga placă poate fi îndoită cu o rază de <5 mm, care este perfect adaptată la designul carcaselor rotunde ale ceasurilor. Prin controlul înălțimii componentelor (cea mai înaltă componentă ≤ 1,2 mm), grosimea totală a plăcii de dezvoltare este comprimată la mai puțin de 2,5 mm, eliberând 30% de spațiu pentru baterie și senzori. Pentru electronica auto, placa de dezvoltare Automotive ADAS se confruntă cu temperaturi ridicate (-40 ℃ ~ +125 ℃), vibrații (accelerație 50g) din mediul dur, tehnologia SMT prin miniaturizare pentru a realiza un aspect compact: utilizarea de 0.5mmpitch BGA pachet cip, cu partea de jos a procesului de umplere (viteza de umplere 50mm / s), în 100mm × 100mm substrat de integrare a 6 AI cip cu 20 Senzor interfață, volumul este redus cu 60% în comparație cu soluția tradițională, și, în același timp, eficiența disipării căldurii este îmbunătățită prin optimizarea distanței componente (≥0.5mm).

Pentru industria aerospațială, plăcile de dezvoltare a încărcăturii utile prin satelit sunt sensibile la greutate (cost per gram>$1000), tehnologia SMT prin adaptarea materialelor ușoare pentru a realiza o descoperire: utilizarea PCB pe bază de aluminiu (densitate 2,7g/cm³) în locul substratului tradițional FR-4, cu o grosime de 0,1 mm a cipului ultra-subțire (greutate <0,1g) de montare, astfel încât greutatea unității de suprafață să reducă greutatea de 40%. Prin algoritmul de optimizare a dispunerii componentelor (soluție de algoritm genetic), 10 straturi de interconexiuni de circuite sunt realizate pe un substrat de 200 mm × 150 mm, ceea ce economisește 20% spațiu în comparație cu dispunerea manuală.