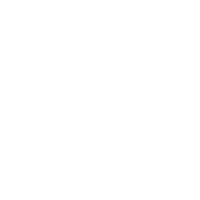

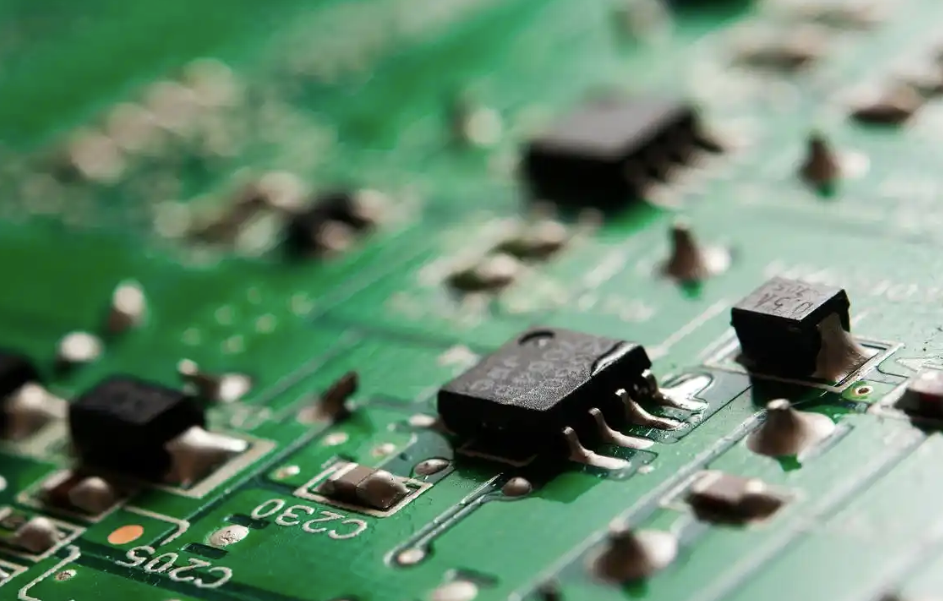

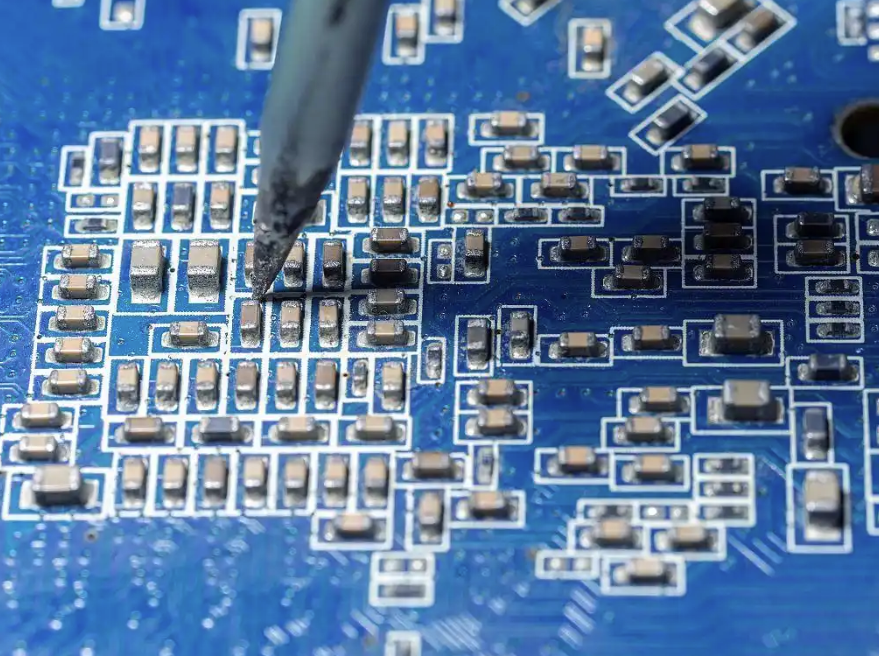

Com o crescimento explosivo dos dispositivos eletrônicos portáteis, a forma de terminal da Internet das Coisas continua a evoluir, a placa de desenvolvimento de semicondutores, como a principal portadora do sistema eletrônico, está enfrentando o desafio triplo de "tamanho menor, maior integração e melhor desempenho". Como o principal processo de processamento de PCBA, a tecnologia de colocação SMT por meio da adaptação da miniaturização de componentes, inovação do processo de montagem de alta densidade e avanços na capacidade de integração tridimensional, para se tornar o principal mecanismo para resolver os problemas de miniaturização da placa de desenvolvimento, para promover seus eletrônicos de consumo, eletrônicos automotivos, aeroespaciais e outros campos para alcançar a forma da revolução. Primeiramente, gostaríamos de discutir a física por trás da base da miniaturização dos componentes elétricos. A principal vantagem da tecnologia de colocação SMT é que ela rompe as limitações de tamanho da inserção tradicional através de orifícios e fornece um suporte físico confiável para componentes eletrônicos ultraminiaturais. As modernas máquinas de colocação podem colocar com precisão componentes de chip de tamanho 0201 (0,6 mm x 0,3 mm) ou até 01005 (0,4 mm x 0,2 mm), com precisão de colocação de ±50μm, para atender aos requisitos de alinhamento de pacotes QFP com passo de pino de 0,3 mm. Graças à série de máquinas pick and place NT-P5 da Nectec, ela é capaz de obter um processamento flexível dos componentes de chip de tamanho 0201 usando a tecnologia de transformação de suporte de design modular. Esse recurso permite que as placas de desenvolvimento de semicondutores aumentem a densidade do layout dos componentes de 5 a 10 vezes: nas placas de desenvolvimento de banda base de smartphones, por meio da combinação de capacitores MLCC de tamanho 0402 e chips embalados em LGA com passo de 0,5 mm, a unidade de centímetro quadrado pode ser integrada com mais de 50 componentes ativos e 200 passivos, o que representa mais de 3 vezes a densidade de integração em comparação com o processo de inserção tradicional.

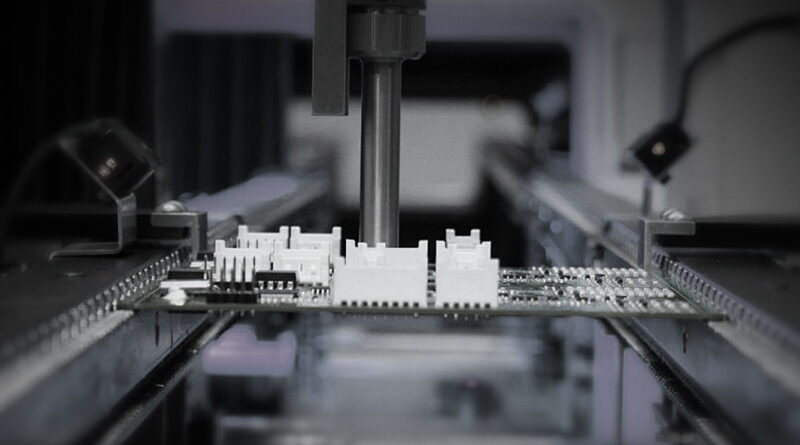

No próximo tópico, discutiremos a aplicação na vida real desse avanço da tecnologia SMT. Gostaríamos de nos concentrar em três áreas: eletrônicos de consumo, eletrônicos para automóveis e indústria aeroespacial. Primeiro, vamos falar sobre os eletrônicos de consumo. Na placa de desenvolvimento do smartwatch, o processo SMT realiza a espessura de 0,4 mm da placa de circuito impresso flexível e a altura de 0,4 mm dos componentes ultrafinos, como a nossa máquina de coleta e colocação NT-L12 da Nectec, com a tecnologia de montagem de superfície curva (desvio do ângulo de montagem <1°), de modo que toda a placa possa ser dobrada com um raio de <5 mm, o que se adapta perfeitamente ao design de caixas de relógio redondas. Ao controlar a altura dos componentes (o componente mais alto ≤ 1,2 mm), a espessura total da placa de desenvolvimento é comprimida para menos de 2,5 mm, liberando 30% de espaço para a bateria e os sensores. Para eletrônicos automotivos, a placa de desenvolvimento do ADAS automotivo enfrenta alta temperatura (-40 ℃ ~ +125 ℃), vibração (aceleração de 50g) do ambiente hostil, tecnologia SMT por meio de miniaturização para obter um layout compacto: o uso de chip de pacote BGA de 0.5mmpitch BGA, com a parte inferior do processo de enchimento (velocidade de enchimento de 50mm / s), na integração de substrato de 100mm × 100mm de 6 chips AI com interface de 20 sensores, o volume é reduzido em 60% em comparação com a solução tradicional e, ao mesmo tempo, a eficiência da dissipação de calor é aprimorada por meio da otimização do espaçamento dos componentes (≥0,5mm).

Para o setor aeroespacial, as placas de desenvolvimento de carga útil de satélite são sensíveis ao peso (custo por grama>$1000), a tecnologia SMT por meio da adaptação de material leve para alcançar um avanço: o uso de PCB à base de alumínio (densidade 2,7g/cm³) em vez do substrato FR-4 tradicional, com 0,1 mm de espessura de montagem de chip ultrafino (peso <0,1g), de modo que o peso da área da unidade reduza o peso de 40%. Por meio do algoritmo de otimização de layout de componentes (solução de algoritmo genético), 10 camadas de interconexões de circuitos são realizadas em um substrato de 200 mm x 150 mm, o que economiza 20% de espaço em comparação com o layout manual.