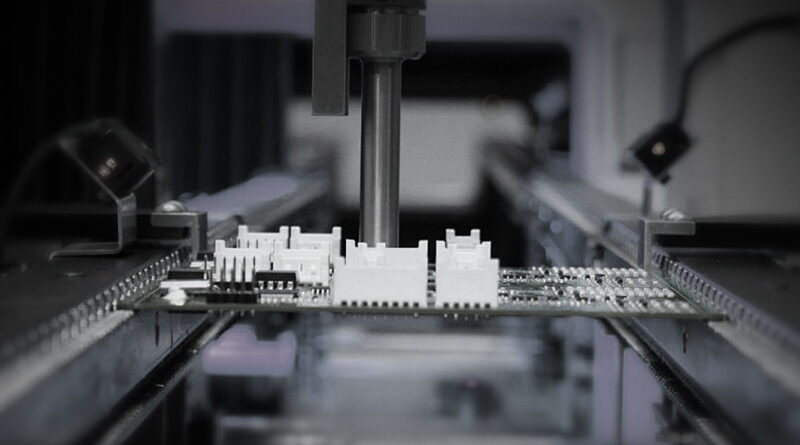

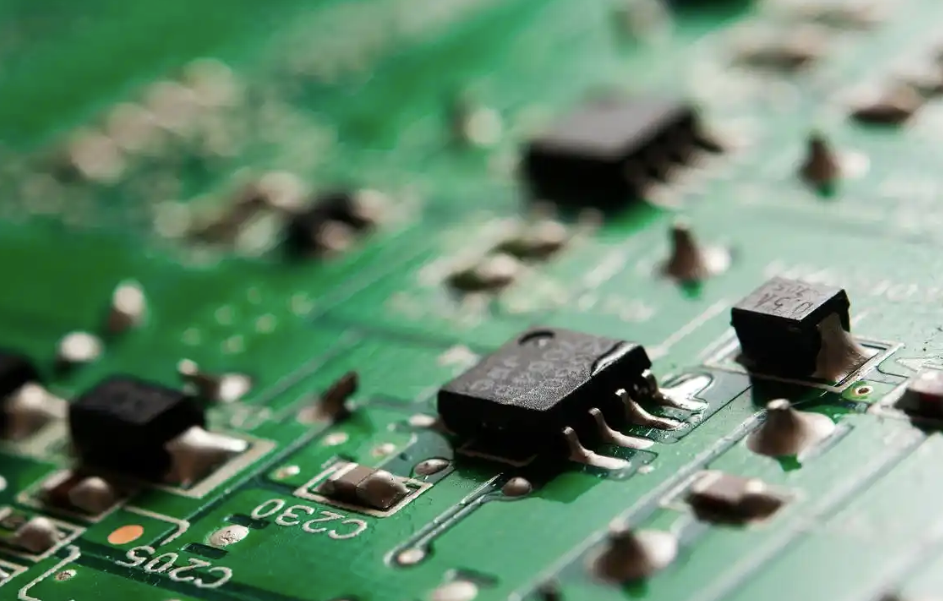

En el crecimiento explosivo de los dispositivos electrónicos portátiles, la forma de terminal del Internet de las Cosas sigue evolucionando, la placa de desarrollo de semiconductores como soporte central del sistema electrónico se enfrenta al triple reto de "menor tamaño, mayor integración, mayor rendimiento". Como el proceso central de procesamiento de PCBA, la tecnología de colocación SMT a través de la adaptación de la miniaturización de componentes, la innovación del proceso de montaje de alta densidad y los avances en la capacidad de integración tridimensional, para convertirse en el motor clave para resolver los problemas de miniaturización de la placa de desarrollo, para promover su electrónica de consumo, electrónica automotriz, aeroespacial y otros campos para lograr la forma de la revolución. En primer lugar, nos gustaría discutir acerca de la física detrás de la base de la miniaturización de los componentes eléctricos. La principal ventaja de la tecnología de colocación SMT es que rompe con las limitaciones de tamaño de la inserción tradicional de orificios pasantes y proporciona un soporte físico fiable para componentes electrónicos ultraminiatura. Las máquinas de colocación modernas pueden colocar con precisión componentes de chip de tamaño 0201 (0,6 mm x 0,3 mm) o incluso 01005 (0,4 mm x 0,2 mm), con una precisión de colocación de ±50μm, para cumplir los requisitos de alineación de los paquetes QFP de 0,3 mm de paso de patilla. Gracias a nuestra máquina pick and place Nectec de la serie NT-P5, es capaz de lograr un procesamiento flexible de los componentes de chip de tamaño 0201 utilizando la tecnología de transformación de soporte de diseño modular. Esta capacidad permite a las placas de desarrollo de semiconductores aumentar la densidad de disposición de componentes entre 5 y 10 veces: en las placas de desarrollo de banda base para smartphones, mediante la combinación de condensadores MLCC de tamaño 0402 y chips empaquetados en LGA de 0,5 mm de paso, la unidad de centímetro cuadrado puede integrarse con más de 50 componentes activos y 200 pasivos, lo que supone más de 3 veces la densidad de integración en comparación con el proceso de inserción tradicional.

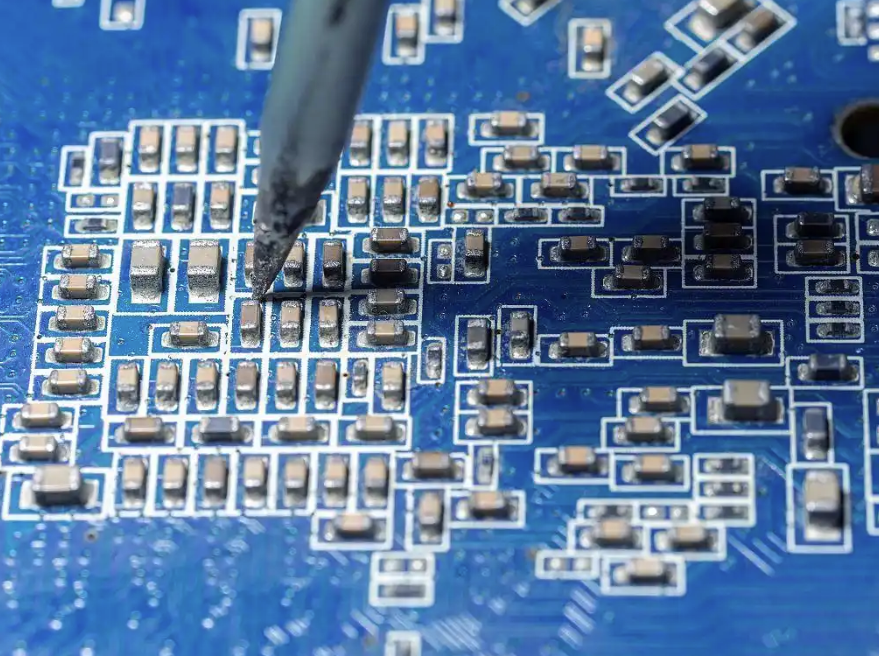

En el próximo tema, hablaremos de la aplicación en la vida real de este avance de la tecnología SMT. Hay tres áreas en las que nos gustaría centrarnos: electrónica de consumo, electrónica del automóvil e industria aeroespacial. En primer lugar, hablaremos de la electrónica de consumo. En la placa de desarrollo del smartwatch, el proceso SMT realiza el grosor de 0,4 mm de la placa de circuito impreso flexible y la altura de 0,4 mm de los componentes ultrafinos, como nuestra máquina de pick and place NT-L12 de Nectec, con la tecnología de montaje de superficie curvada (desviación del ángulo de montaje <1°), de modo que toda la placa puede doblarse con un radio de <5 mm, que se adapta perfectamente al diseño de las cajas redondas de los relojes. Al controlar la altura de los componentes (el componente más alto ≤ 1,2 mm), el grosor total de la placa de desarrollo se comprime a menos de 2,5 mm, liberando 30% de espacio para la batería y los sensores. Para la electrónica del automóvil, Automotive ADAS placa de desarrollo frente a la alta temperatura (-40 ℃ ~ +125 ℃), vibración (50g de aceleración) del ambiente áspero, la tecnología SMT a través de la miniaturización para lograr un diseño compacto: el uso de 0.5mmpitch chip de paquete BGA, con la parte inferior del proceso de llenado (velocidad de llenado de 50 mm / s), en la integración de sustrato de 100 mm × 100 mm de 6 AI chip con interfaz de 20 sensores, el volumen se reduce en 60% en comparación con la solución tradicional, y al mismo tiempo, la eficiencia de disipación de calor se mejora a través de la optimización de la separación de los componentes (≥0,5 mm).

Para la industria aeroespacial, las placas de desarrollo de carga útil de satélites son sensibles al peso (coste por gramo>$1000), la tecnología SMT a través de la adaptación de materiales ligeros para lograr un gran avance: el uso de PCB a base de aluminio (densidad 2,7g/cm³) en lugar del tradicional sustrato FR-4, con 0,1mm de espesor de chip ultrafino (peso <0,1g) de montaje, de modo que el peso de la unidad de área para reducir el peso de 40%. Mediante el algoritmo de optimización de la disposición de componentes (solución de algoritmo genético), se realizan 10 capas de interconexiones de circuitos en un sustrato de 200 mm×150 mm, lo que ahorra 20% de espacio en comparación con la disposición manual.